有望加速了嗎!5G 基礎建設因為網路訊號頻率高,需大量建置基地台以滿足覆蓋率,而且越高頻的毫米波頻段訊號消耗越高,還有建置高成本等問題。這幾點中空玻璃球都解決了~

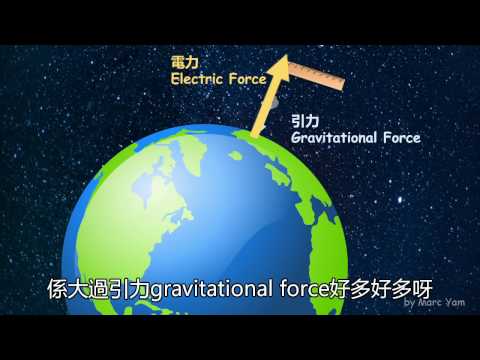

同時也有1部Youtube影片,追蹤數超過2萬的網紅Marc Yam,也在其Youtube影片中提到,Section IV Electricity and Magnetism 4.1 Electrostatics Coulomb's Law 重溫: Universal Gravitation 萬有引力 https://youtu.be/22BA-BQFbqg ***感謝Charles Lee指出...

介電常數 在 UNIKO's Hardware Facebook 的精選貼文

Intel 今日公開了現在及未來製程與封裝技術發展規劃,看起來前途一片光明~

#INTEL #製程 #封裝 #發展 #UH

介電常數 在 台灣應用材料公司 Applied Materials Taiwan Facebook 的最讚貼文

【上課囉 📣 邏輯晶片大師班 幫你更深入了解半導體】

應材工程副總裁Uday Mitra博士說「進入3nm以下的世界,材料工程是關鍵。」

邏輯晶片大師課程,分別由三位講者,

講述尺寸微縮時,半導體先進製程的挑戰與材料工程解決方法!

想快速閱讀微縮先進邏輯晶片解決方案,快看精華版 ✨ https://bit.ly/3hQNAbT

想直接上課,請進邏輯晶片大師班 ✨ https://bit.ly/3qV4SbQ

想知道三位講者各別討論的議題,繼續往下讀重點整理!

1️⃣首先由Mike Chudzik博士揭開序幕,

人工智慧、大數據和物聯網持續推動半導體需求,

實現微縮需克服的物理限制,包括:

提升電晶體開關的切換速度、

FinFET微縮時面臨的鰭彎曲問題、

高介電常數金屬閘極(HKMG)的多層接面的微縮,以及

閘極全環(Gate All Around, GAA)結構的製程技術。

全文請見:https://bit.ly/3hOH3hE

2️⃣接著,Mehul Naik博士提到當尺寸微縮至3nm以下,

內部連接介面電阻是最大的挑戰,

電晶體傳輸功率的方式是影響微縮的關鍵因素,

背向功率傳輸網絡(backside power delivery network)是新的解決方案,

能降低電壓損失、縮小電晶體面積、為導線預留更多空間!

全文請見:https://bit.ly/36qlyyg

3️⃣最後,Regina Freed博士探討設計圖形的可變型,

設計技術協同最佳化 (Design & Technology Co-Optimization, DTCO)是先進製程微縮的關鍵,

讓工程師能用新材料、新設計突破節點限制,

就好比蓋房子,當面積有限,

我們可以增加第二層、地下室,

而不是犧牲某些區域以擴大的空間,

DTCO允許更巧妙的2D & 3D 設計,

能維持相同間距,同時增加邏輯密度。

全文請見:https://bit.ly/3hJGm9y

介電常數 在 Marc Yam Youtube 的精選貼文

Section IV Electricity and Magnetism

4.1 Electrostatics

Coulomb's Law

重溫:

Universal Gravitation 萬有引力

https://youtu.be/22BA-BQFbqg

***感謝Charles Lee指出錯誤,現已修正重新上載***

介電常數 在 測試介電常數,利用阻抗分析儀分析材料的介電損耗 ... - YouTube 的推薦與評價

介電常數 又稱之介質常數或是電容率,是一種表示絕緣能力特性的一個係數,以字母ε表示,單位為法/米。介電常數 ... ... <看更多>

介電常數 在 [請問] 半導體的介電常數- 看板ChemEng - 批踢踢實業坊 的推薦與評價

※ [本文轉錄自 ask 看板 #1DxVSFs7 ]

作者: GYLKKBOY (加油!!!) 站內: ask

標題: [請問] 半導體 的 介電常數

時間: Tue Jun 7 18:01:49 2011

抱歉 網路實在太雜亂了

我想請問大家知道哪些半導體的介電常數嗎 10~14的

我目前只知道 砷化鎵 (11.4) 矽材(silicon) (13)

請知道的前輩告知一下 感恩啦~~

或者有哪個版在討論這一類相關的嗎 ?

--

--

※ 發信站: 批踢踢實業坊(ptt.cc)

◆ From: 140.112.39.182

--

--

※ 發信站: 批踢踢實業坊(ptt.cc)

◆ From: 140.112.39.182

... <看更多>